≤ъ∆Ј÷––ƒ ”¶”√Јљ∞Є ЉЉ хќƒ’™÷ Ѕњ±£÷§≤ъ∆Ј—°–Ќ ѕ¬‘Ў÷––ƒ“µƒЏґѓћђ —°–Ќ∞п÷ъ ∆Ј≈∆љй…№ ≤ъ∆Ј“їјј Ѕ™ѕµќ“√«

- і≈÷¬…мЋхќї“∆іЂЄ–∆чќї“∆≤вЅњ—–Њњ”л µѕ÷

- јі‘і£Ї»ьЋєќђіЂЄ–∆чЌш ЈҐ±н”Џ 2014/8/18

°°°°’™“™£Їїщ”Џі≈÷¬…мЋхќї“∆іЂЄ–∆чµƒќї“∆≤вЅњ‘≠јн.ћ÷¬џЅЋќї“∆ЬyЅњµƒЈљЈ®”л µѕ÷°£Ќ®єэ≤вЅњЈҐ…д¬ц≥е”лїЎ≤®¬ц≥еµƒ ±Љд≤оЉ∆ Ћгїоґѓі≈ћъµƒќї÷√°£їщ”ЏFPGA∆чЉю…иЉ∆ЅЋ э„÷“∆ѕа¬ц≥еЉ∆ эЈљ љґ‘ ±Љдљш––ЊЂ»Ј≤вЅњ.Є√ЈљЈ®ґ‘”ЏћбЄя≤вЅњќї“∆ЊЂґ».љµ µЌ≤вЅњѕµЌ≥ґ‘Єя∆µµƒ“™«у.ґ‘ћбЄяѕµЌ≥ќ»ґ®–‘ЇЌњєЄ…»≈ƒ№Ѕ¶”–÷Ў“™“в“е°£

°°°°єЎЉьі £Їі≈÷¬…мЋх°° э„÷“∆ѕа ±Љд≤вЅњ FPGA

°°°°1°°“э —‘

°°°°і≈÷¬…мЋхќї“∆іЂЄ–∆ч «“ї÷÷“‘і≈÷¬≈§„™≤®ќ™іЂ≤• √љљйµƒіЂЄ–∆ч£ђ’в÷÷іЂЄ–∆ч∞≤„∞Љтµ•°ҐЈљ±г£ђƒ№≥– №Єя ќ¬°ҐЄя—єЇЌЄя’сµіµƒїЈЊ≥°£єгЈЇ”¶”√”Џ“„±ђ°Ґ“„»Љ“„ї” ЈҐ°Ґ”–Єѓ іµƒ≥°Їѕ£ђµЂ‘ЏєъƒЏ…иЉ∆ЇЌ”¶”√µƒґЉ±»љѕ…ў°£ ќƒ÷–їщ”Џі≈÷¬…мЋхќї“∆іЂЄ–∆чµƒ‘≠јн£ђ≤ы цЅЋ“ї÷÷њ… “‘ћбЄяі≈÷¬…мЋхќї“∆іЂЄ–∆чЊЂґ»µƒќї“∆≤вЅњЈљЈ®°£

°°°°2°°і≈÷¬…мЋхќї“∆іЂЄ–∆чµƒ‘≠јн

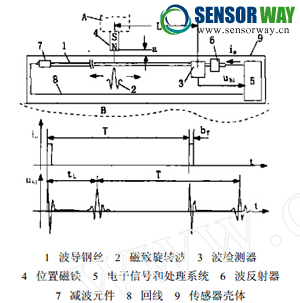

°°°°і≈÷¬…мЋхќї“∆іЂЄ–∆ч(M agnetostrictive Position Sensor)»зЌЉ1Ћщ Њ£ђ÷ч“™”…≤®µЉЄ÷Ћњ1£ђќї÷√і≈ћъ4, ≤®Љм≤в∆ч3ЇЌµз„”ѕµЌ≥5„й≥…°£ќї÷√і≈ћъЌ®≥£„∞‘Џ“ї Єц‘Ћґѓ≤њЉюA…ѕ£ђґшіЂЄ–∆ч÷чће‘т„∞‘Џ“їЄцєћґ®µƒ≤њЉюB…ѕ°£іЂЄ–∆чє§„ч ±£ђµз„”–≈Ї≈ЇЌі¶јнѕµЌ≥5“‘ ±Љд ЉдЄфќ™T1ЈҐЄші≈÷¬≤®µЉЄ÷Ћњ1µƒЉ§јш¬ц≥еµзЅчL°£Є√ ¬ц≥еµзЅчљЂ≤ъ…ъ“їЄцќІ»∆≤®µЉЄ÷Ћњ1µƒ–э„™і≈≥°°£ќї ÷√і≈ћъ4“≤≤ъ…ъ“їЄцєћґ®µƒі≈≥°°£‘Џ’вЅљЄці≈≥°µƒ’э љї„ч”√ѕ¬£ђ≤®µЉЄ÷Ћњ≤ъ…ъі≈÷¬µѓ–‘…мЋх£ђ–ќ≥…“їЄці≈÷¬ –э„™≤®2°£Є√–э„™≤®—Ў„≈≤®µЉЄ÷Ћњ“‘2800m/SµƒЋўґ» ѕтЅљ±яіЂ≤•°£µ±ЋьіЂµљ≤®µЉЄ÷Ћњ“їґЋµƒ≤®Љм≤в∆ч3 ± ±ї„™її≥…µз–≈Ї≈Ua°£Ќ®єэ≤вЅњі≈÷¬–э„™≤®і”ќї÷√і≈ћъ 4іЂµљ≤®Љм≤в∆ч3µƒ ±ЉдTOЊЌƒ№»Јґ®ќї÷√і≈ћъЇЌ≤® Љм≤в∆ч÷ЃЉдµƒЊајл°£’в—щ£ђµ±≤њЉюAЇЌB≤ъ…ъѕаґ‘‘Ћ ґѓ£ђЌ®єэі≈÷¬–э„™≤®ќї“∆іЂЄ–∆чЊЌњ…“‘»Јґ®≤њЉюAµƒќї÷√ЇЌЋўґ»°£

°°°°3°°ќї“∆≤вЅњ‘≠јнЇЌ≥£єжЈљЈ®Ј÷ќц

°°°°і≈÷¬…мЋхќї“∆іЂЄ–∆чµƒќї“∆Љ∆ЋгЈ«≥£Љтµ•£ђљЂЋщ≤вЅњµƒ ±Љд≤о≥Ћ“‘і≈÷¬…мЋх≈§„™≤®µƒіЂ≤•Ћўґ»:ќї÷√ = ±≤оx≈§„™≤®іЂ≤•Ћўґ»-Ѕгµгќї÷√(Ѕгµгќї÷√ќ™Ѕг «ш”лЋј«ш÷ЃЇЌ)°£”…”Џі≈÷¬…мЋх≤ƒЅѕ≤…”√‘≤–ќљЎ√жЋњ£ђ ЄщЊЁPochhammerµƒґюќђµѓ–‘јн¬џ£ђ≈§„™≤®‘Џ‘≤љЎ√ж ЄЋ÷–µƒіЂ≤•–ќ љ «єЎ”Џ‘≤÷щ÷––ƒ÷бґ‘≥∆µƒ£ђ∆д≈§„™≤®Ћўci= (G/P)1/2∆д÷–:Gќ™і≈÷¬…мЋх≤ƒЅѕµƒ«–±дƒ£ Ѕњ£ђPќ™і≈÷¬…мЋх≤ƒЅѕµƒ√№ґ»÷µ°£

ЌЉ1 і≈÷¬–э„™≤®ќї“∆іЂЄ–∆чµƒ≤вЅњ‘≠јн

°°°°ƒ«√іќї“∆L= C1 * T°£- L°£(∆д÷–:C1ќ™”¶±д≤®µƒіЂ≤•Ћўґ»Tќ™ ±ЉдЉдЄф£ђLќ™Ѕгµгќї÷√£ђЅгµгќї÷√µ»”Џ Ѕг«ш”лЋј«ш÷ЃЇЌ)°£њ…÷™£ђќї“∆≤вЅњќу≤оAL= Ac1 * T°£+ AT* C1£ђ∆д÷–ґ‘Њяћеµƒ≤®µЉє№јіЋµ£ђ‘Џ“їґ®ќ¬ґ»Јґ ќІƒЏ£ђGЇЌPґЉ «Їгґ®µƒ£ђ“тіЋC1 «Їгґ®µƒ£ђЉіAc1=°££ђ ƒ«√іќї“∆≤вЅњµƒќу≤о÷ч“™”… ±ЉдЅњЉм≤вµƒќу≤оЊцґ®£ђ AL= AT°£* c1£ђ“тґш ±≤оµƒ≤вЅњ «Љ∆Ћгќї÷√ЊЂґ»µƒєЎ Љь°£µз„”ЉЉ хЉ∞Љ∆ЋгїъЉЉ хµƒЈҐ’єќ™ЊЂ»Ј≤вЅњћбє©ЅЋ іуЅњЄя–‘ƒ№°Ґ–°ћеїэµƒ∆чЉюЇЌ÷ЏґаЋгЈ®°£јы”√ѕ÷іъЉ∆Ћг їъЉ∆ эЉ∞µз„”ЉЉ х£ђњ…ґ‘¬ц≥е…щ≤®µƒіЂ≤• ±Љдљш––ЊЂ »Ј≤вЅњ°£Ќ®≥£≤…”√ э„÷µз¬Ј»Ё“„іпµљµЌ‘л…щЇЌЄяЊЂґ» µƒћЎµг°£µз„”µз¬Ј”…Ќв÷√њЎ÷∆∆чћбє©і•ЈҐ–≈Ї≈°£іЂЄ–∆чµз„”љ” ’µз¬Јјы”√і•ЈҐ¬ц≥еЇЌїЎ≤®¬ц≥еµч÷∆≤ъ…ъ“їЄц њн¬ц≥е£ђµч÷∆Їуµƒ¬ц≥ењнґ»”лі≈ћъќї÷√≥…’э±»°£јы”√ э „÷Љ∆ эЈљ љјіґ‘њн¬ц≥ељш––≤вЅњ£ђЉ∆ эє¶ƒ№µƒ µѕ÷ЊЌ «“™±£÷§‘Џі•ЈҐ¬ц≥ењ™ Љ ±Љ∆ э£ђґш‘Џљ” ’µљїЎ≤®–≈ Ї≈ЇуЌ£÷єЉ∆ э°£Ќ®єэЉ∆ э∆чµƒЉ∆ э÷µЊЌњ…“‘Љ∆Ћгќї“∆°£

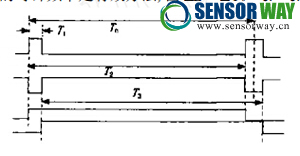

°°°° ±Љд≤о≤вЅњ‘≠јн»зЌЉ2Ћщ Њ°£

°°°°ЌЉ÷–ЅљЄц’≠¬ц≥е–≈Ї≈Ј÷±рќ™і•ЈҐ¬ц≥еЇЌїЎ≤®¬ц ≥е°£јы”√’вЅљЄц’≠¬ц≥е–≈Ї≈µч÷∆≥цјіµƒ¬ц≥ењнґ»Ј÷±р ќ™T2ЇЌT3°£і•ЈҐ–≈Ї≈µƒ ±ЉдT1“—÷™°£»зєыЉ∆ э∆чµƒ ±÷”∆µ¬ ќ™f£ђ÷№∆Џќ™T°£»фґ‘”ЏT2ґќ£ђЉ∆ э∆чµƒЉ∆ э ÷µќ™m2,ґ‘”ЏT3ґќµƒЉ∆ э÷µќ™m3,ƒ«√іT0= (m2+ m3) * T/2+ T1/2;”…”Џ≤…”√ э„÷Љ∆ эЈљ љ≤вЅњ£ђЉ∆ э ќу≤оќ™°ј 1£ђ ±Љдќу≤оќ™°јT£ђ ±ЉдЈ÷±жЅ¶‘љЄя,ќї“∆≤в Ѕњќу≤о‘љ–°£ђЋщ“‘ЄяЈ÷±жЅ¶µƒ ±ЉдЅњЉм≤вґ‘іЂЄ–∆ч µ ѕ÷ЄяЊЂґ»≤вЅњЇ№єЎЉь°£»зєы“™ћбЄя ±ЉдЈ÷±жЅ¶,ћбЄяЉ∆ э∆чµƒ ±÷”∆µ¬ «”––І∞мЈ®£ђ”…AL= AT°£* c1= c1/fЌЉ2 ±Љд≤о≤вЅњ‘≠јнЌЉ ∆д÷–:fќ™Љ∆ э∆чµƒЉ∆ э∆µ¬ °£

°°°°ґ‘”Џ±ЊіЂЄ–∆чµƒ≤ƒЅѕ£ђc1= 280Qm/s,»зєыѕµЌ≥“™ «уќї“∆„оіуќу≤оќ™20jum£ђ‘т£Ї f= 2800* 106/20= 14CMHz »зєыѕµЌ≥Љ∆ э ±÷”∆µ¬ ќ™5(MHz,‘т ±Љдќу≤оќ™ °ј2Qns,ќї“∆„оіуќу≤оќ™56_°£”…іЋњ…Љы£ђ»зєыіпµљѕµ Ќ≥ЄяЊЂґ»“™«у£ђ’в÷÷Љтµ•µƒЉ∆ эЈљ љ–и“™Ї№Єяµƒ ±÷” ∆µ¬ £ђґш‘Џ’в—щµƒЄя∆µ„іћђѕ¬£ђѕµЌ≥њєµзі≈Јш…дЄ…»≈ƒ№ Ѕ¶”÷ґ‘ѕµЌ≥µƒ≥…±Њћб≥цЅЋЄьЄяµƒ“™«у°£»зєы≤ї є…иЉ∆ ѕЁ»лЅљƒ—Њ≥µЎ£ђ”¶Є√—∞«у–¬µƒ≤вЅњЈљ љ°£

°°°°4°° э„÷ѕа“∆¬цњн ±Љд≤вЅњЈљЈ®

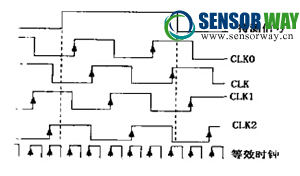

°°°°Ћщќљ“∆ѕа «÷Єґ‘”ЏЅљ¬ЈЌђ∆µ–≈Ї≈,“‘∆д÷–“ї¬Јќ™ ≤ќњЉ–≈Ї≈,Ѕн“ї¬Јѕаґ‘”ЏЄ√≤ќњЉ–≈Ї≈„ц≥ђ«∞їт÷ЌЇуµƒ “∆ґѓ–ќ≥…ѕаќї≤о°£ э„÷“∆ѕаЌ®≥£≤…”√—” ±ЈљЈ®,“‘—” ± µƒ≥§ґћјіЊцґ®Ѕљ э„÷–≈Ї≈Љдµƒѕаќї≤о,“‘Ћƒѕа“∆ќ™јэ£ђ ≤ы ц э„÷ѕа“∆¬цњнµƒ≤вЅњ£ђ»зЌЉ3Ћщ Њ°£

°°°°ЌЉ3 э„÷ѕа“∆¬цњн ±Љд≤вЅњ‘≠јнЌЉ

°°°° ±÷”–≈Ї≈CLK0“јіќљш––90°г“∆ѕа£ђµ√µљCLK£ђ CLK1ЇЌCLK2,’вЋƒ¬Ј ±÷”–≈Ї≈«эґѓЋƒЄцѕаЌђµƒЉ∆ э∆чґ‘іэ≤в–≈Ї≈љш––Љ∆ э°£…и ±÷”∆µ¬ ќ™f£ђ÷№∆Џќ™T£ђЋƒ ЄцЉ∆ э∆чµƒЉ∆ э÷µЈ÷±рќ™m0,m,m1,m2,‘т„оЇуµƒ¬ц њн≤вЅњ÷µќ™:T0= (m0+ m+ m1+ m2) * T/4°£њ…“‘њі µљ£ђ’в÷÷Љ∆ эЈљ љµƒ ±÷”∆µ¬ ѕаµ±”ЏљЂ‘≠ ЉЉ∆ э ±÷” љш––4±ґ∆µ£ђ“‘4fµƒ∆µ¬ љш––≤вЅњ£ђ“тґшљЂ≤вЅњЊЂґ» “≤ћбЄяµљ‘≠јіµƒЋƒ±ґ°£љЂ э„÷ѕа“∆¬цњн ±Љд≤вЅњЈљЈ® ”√”Џ≤вЅњЌЉ2÷–µƒЅљЄц“—µч÷∆–≈Ї≈£ђ‘тњ…“‘ЉЂіуµƒћб ЄяѕµЌ≥ЊЂґ»£ђЄƒ…∆ѕµЌ≥–‘ƒ№°£»зєы‘≠јіµƒѕµЌ≥ ±÷”ќ™ 50MHz£ђѕµЌ≥µƒµ»–І ±÷”ќ™200MHz£ђ»зєы≤їњЉ¬«Єч¬Ј Љ∆ э ±÷”Љдµƒѕаґ‘—”≥ў ±Љдќу≤о£ђ∆д≤вЅњµƒ„оіуќу≤о љµќ™‘≠јіµƒЋƒЈ÷÷Ѓ“ї£ђљцќ™5¶ћm°£Ќђ ±£ђ’в÷÷ЈљЈ®±£÷§ЅЋ’ыЄцµз¬Јµƒ„оіує§„ч∆µ¬ »‘ќ™f£ђ±№√вЅЋ ±÷”ћбЄя ішјіµƒ“їѕµЅ–ќ ћв°£

°°°°5°° э„÷ѕа“∆ ±Љд≤вЅњµƒ µѕ÷

°°°°”…”ЏіЂЄ–∆ч∆чЉю”––І≥§ґ»ќ™150mm£ђ‘т„о≥§ ±≤о ќ™ Tmax= 15mm/2800m (s)= 53 57ќҐ√лѕµЌ≥≤…”√ 50MHz ±÷”£ђ‘т„оіуЉ∆ э÷µќ™Mmax°÷2680,ќ™ЅЋ±г”Џ”л э„÷і¶ јнѕµЌ≥љ”њЏ£ђ≤…”√∞ЋќїЉ∆ э∆ч“м≤љіЃЅђЉ∆ э£ђ‘тґ‘”Џ√њ “ї¬Ј ±÷”–и“™4ЄцЉ∆ э∆ч°£‘ЏѕµЌ≥ґЅ»° ±£ђ“јіќі”Єяµљ µЌґЅ»°8ќїЉ∆ э÷µ°£”…”Џ ±÷”ќ™5(MHz£ђ≤ъ…ъ90°гµƒѕа “∆–и“™µƒ ±Љд—” ±ќ™5ns°£

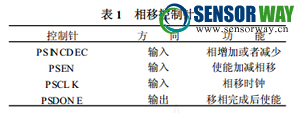

°°°° э„÷ѕа“∆¬цњн ±Љд≤вЅњµƒїщ±Њµг‘Џ”Џ ±÷”–≈Ї≈µƒ ѕаќї—”≥ў,ґшѕаќї—”≥ў‘Џ µЉ µѕ÷÷– «Ќ®єэ ±Љд≤®–ќ µƒ—”≥ўјі µѕ÷£ђ“тґш µѕ÷„Љ»ЈµƒЇЌ»Јґ®µƒµз¬Ј—”≥ўґ‘ ”ЏЄ√ƒ£–ЌµƒЌк’ы–‘”–÷Ў“™„ч”√°£ µѕ÷—” ±”–ґа÷÷ЈљЈ®£ђ »з≤…”√Ј÷ЅҐ‘™Љю µѕ÷£ђµЂ’в÷÷ЈљЈ®іж‘Џµз¬ЈЄі‘”њ…њњ –‘≤оµ»»±µг°£ќƒ÷–≤…”√FPGA∆чЉю µѕ÷ЄяЊЂґ»µƒ—” ± Њя”–µз¬ЈЉтµ•°Ґє¶ƒ№«њ°Ґ–ёЄƒЈљ±гЇЌњ…њњ–‘Єяµ»”≈µг°£ RTEX-IIѕµЅ–FPGA∆чЉю”–4~12Єц э„÷ ±÷”є№јн ∆чDCM,√њЄцDCMґЉћбє©ЅЋ”¶”√ЈґќІєг°Ґє¶ƒ№«њіу µƒ ±÷”є№јнє¶ƒ№°£»з ±÷”»• ±÷Ќ°Ґ∆µ¬ Їѕ≥…Љ∞“∆ѕаµ»°£ Ћьјы”√—” ±Ћшґ®їЈDLL£ђѕы≥э ±÷”ЇЄ≈ћЇЌƒЏ≤њ ±÷”“э љ≈Љдµƒ∞Џґѓ£ђЌђ ±Ћьїєћбє©ґа÷÷ ±÷”њЎ÷∆ЉЉ х£ђ µѕ÷ ± ÷”÷№∆ЏƒЏ»ќ“вќї÷√µƒЊЂ»ЈѕаќїњЎ÷∆£ђЈ«≥£ Їѕ ±–тќҐ µч”¶”√£ђґ‘…и÷√ЇЌ±£≥÷ ±–тґ‘„ЉЈ«≥£єЎЉь°£DCMѕа“∆ Њя”–њ…±дѕа“∆ЇЌєћґ®ѕа“∆Ѕљ÷÷ƒ£ љ°£…иЉ∆÷–£ђ”…”Џ—” ± Ѕњ”…”√їІЌв≤њ д»лћбє©,є ≤…”√њ…±дѕа“∆ƒ£ љ°£‘Џњ…±д ѕа“∆ƒ£ љ÷–£ђ”√їІњ…“‘ґѓћђµЎЈіЄіљЂѕаќїѕт«∞їтѕтЇу “∆ґѓ д»л ±÷”÷№∆Џµƒ1/256°£њ…±дѕа“∆ƒ£ љ÷–,ѕа“∆њЎ÷∆’л»з±н1Ћщ Њ°£

µ±PSEN–≈Ї≈”––І,‘тѕа“∆÷µњ…“‘”…”лѕа“∆ ±÷” PSCLKЌђ≤љµƒPSNCDEC–≈Ї≈Њцґ®ґѓћђµЎЙИЉ”їтЉх …ў°£…иЉ∆÷–ѕа“∆ ±÷””… д»л ±÷”ћбє©£ђPSDONE д≥ц –≈Ї≈”лѕа“∆ ±÷”Ќђ≤љ£ђЋь д≥ц“їЄцѕа“∆ ±÷”÷№∆ЏµƒЄя µз∆љ±н Њѕа“∆“—Њ≠Ќк≥…£ђЌђ ±±н Њ“їЄц–¬µƒѕа“∆њ…“‘ њ™ Љ°£ д»л ±÷”Њ≠єэDCM“∆ѕаµз¬Ј“∆ѕаЇу£ђµ√µљЋщ–и —” ±÷ЃЇуµƒ ±÷” д≥ц°£…иЉ∆≤…”√„‘ґ•ѕтѕ¬µƒ…иЉ∆ЈљЈ®, ≤…”√”≤Љю√и ц”п—‘VHDLЌк≥…DCM“∆ѕа°Ґ„іћђїъњЎ ÷∆Љ∞≤ќ э д»л»эіує¶ƒ№ƒ£њйµƒ…иЉ∆ д»л°£DCMµƒѕа“∆ ƒ£ љќ™њ…±дѕа“∆ƒ£ љ°£ЄщЊЁ”√їІ д»лµƒЋщ–и—” ±Ѕњ£ђ‘Џ -64~+ 64÷ЃЉд»°“їЄц’ы эѕа“∆÷µ£ђЌ®єэ ±÷”—°‘с∆ч —°‘с”√CLK0°ҐCLK1 µѕ÷0- 10nsµƒґа÷÷ ±—”°£ќƒ÷– ≤…”√6ЄцDCM£ђЅљЄц“ї„й,√њ“ї„йDCM µѕ÷90°гµƒѕа “∆£ђљЂ»э„йіЃЅђ£ђЋƒЄцљЏµгµƒ д≥цЊЌЈ÷±р «‘≠ Љ ±÷”°Ґ ѕа“∆90 °г ±÷”°Ґѕа“∆180 °г ±÷”°Ґѕа“∆270 °г ±÷”°£ µЉ …ѕ£ђ ”…”ЏFPGA∆чЉю±а≥ћµƒЈљ±г–‘,њ…“‘≥дЈ÷јы”√’в÷÷ћЎ µг£ђ“‘ µѕ÷Єьґа±ґ эµƒ±ґ∆µ£ђ6±ґ∆µ°Ґ9±ґ∆µ…х÷ЅЄьіу±ґ эµƒ±ґ∆µµ»µ»£ђ µѕ÷‘≠јн «“ї—щµƒ£ђЊяће”¶ЄщЊЁ µЉ “™ «ујі„ц°£”…”Џ∆™Јщ‘≠“т£ђґ‘VHDL±а≥ћЉ∞∆діъ¬л≤ї‘ў„Є ц°£

°°°°6°°љб ¬џ

°°°°ќƒ÷–ћб≥цµƒЈљЈ® µЉ …ѕ «ґ‘“ї¬Јїщ„Љ ±÷”јы”√ѕа “∆≤ъ…ъЉЄ¬Јµ» ±≤оµƒ ±÷”љш––Љ∆ э£ђЋщ“‘Є√ЉЉ хµƒєЎ Љьќ ћв‘Џ”Џѕа“∆ЊЂ»Ј£ђґшґ‘”ЏЉ∆ э∆чµƒ“™«у≤ї «ћЂЄя°£ ’в—щјы”√FPGAЌк»Ђњ…“‘¬ъ„г≤ќ э“™«у£ђґш«“Њя”–ће їэ–°°Ґє¶ЇƒµЌ°Ґ–‘ƒ№ќ»ґ®°Ґ…иЉ∆µч ‘Јљ±гµ»”≈µг°£ƒ£ƒвµƒ “∆ѕа∆чќёЈ®іпµљ“™«у£ђ÷їƒ№јы”√ э„÷“∆ѕа∆чЉюјі¬ъ„г ЊЂґ»“™«у£ђµЂƒњ«∞Є√∆чЉюЉџЄсЈ«≥£Єя£ђ“ї∞гƒ—“‘љ” №°£ »зєыƒ№єїјы”√FPGA’в—щµƒњ…±а≥ћ∆чЉю„ц≥цЄяЊЂґ» µƒ э„÷“∆ѕаµз¬Ј±ЎљЂ”–ЉЂЄяµƒјы”√Љџ÷µ°££®„ч’я£Їјо«м…љ≈Ћ»’√фіч пєв—о”ј≤≈£©

°°°°„™‘Ў«л„Ґ√чјі‘і£Ї»ьЋєќђіЂЄ–∆чЌш£®www.sensorway.cn£©

- »зєы±Њќƒ ’¬ЉµƒЌЉ∆ђќƒ„÷«÷ЈЄЅЋƒъµƒ»®“ж£ђ«лЉ∞ ±”лќ“√«Ѕ™ѕµ£ђќ“√«љЂ‘Џ24ƒЏЇЋ µ…Њ≥э£ђ–ї–ї£°