- 基于FPGA的多传感器管道内漏磁检测系统

- 来源:赛斯维传感器网 发表于 2014/12/2

摘要:

针对传统管道漏磁检测器检测精度的不足,提出了新式的基于FPGA的高精度管道漏磁检测系统设计,以适应813 mm管径的管道检测任务。主要介绍了系统逻辑设计,实现了多达400路传感器漏磁 检测信号的采集与存储。该设计融合了多种总线协议,可有效解决管道漏磁检测中的采集速率、功耗和精 度的问题。经实验验证,方案切实可行,为设计高精度管道漏磁检测系统提供了新的解决方案。

关键词:漏磁检测;现场可编程门阵列;SPI总线;LVDS串行收发器;

0 引言

铁磁性油气输送管道在长期使用后会因内外因素而造 成管壁腐蚀。腐蚀导致管道的输送安全系数日益降低,如 果缺陷处出现泄露不及时处理,极其可能出现严重的后果, 对管道的安全运行造成潜在的危机。管道内漏磁检测技术是利用漏磁检测原理,使用霍尔传感器检测磁化后的管道,达到缺陷检测的目的。目前,传 统管道漏磁检测器对于缺陷的探测、描述、定位及确定大小 的可靠性仍不稳定,不精确,需要改进的余地很大2。这 是因为传统的管道内检测器传感器数量较少,无法进行高 精度的缺陷检测,系统中传感器数据采集存储是依次进行的,一方面效率低,可靠性低,另一方面,功耗大,系统无法 进行长距离检测。

本文针对这些问题,采用多级的现场可编程门阵列(FPGA),利用其高速的并行处理能力,灵活可变的现场可 编程能力以及丰富的IP核资源,实现400只霍尔型传感器同时采集数据并及时存储,满足了高精度管道内漏磁检测器的所需精度要求。

1 系统概述

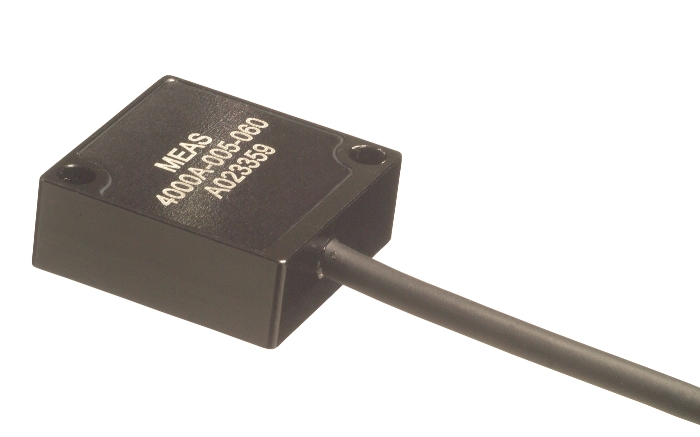

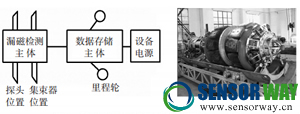

根据本系统设计的管道漏磁检测器外部为圆柱形结 构,可以分为漏磁检测、数据存储和设备电源3个部分,结构示意图如图1所示。漏磁检测主体外的圆周上均匀布置了5个集束器和80个检测探头,每个探头包含不同摆放方 向的5只霍尔传感器和控制采集的单片机,即共有400只 霍尔传感器同时进行信号采集,以获得高精度的管道检测数据;主控FPGA的PCI板卡与PC104-PLUS板卡作为数据 存储主体,确保大量传感器数据的传输与存储,后端为设备 电源部分;在数据存储主体部分的两侧安装有里程轮,用于记录内检测器走过的距离,并在运行中发送方波信号提示系统采集数据。

图1管道内检测器系统结构图与实物图

2 系统硬件组成

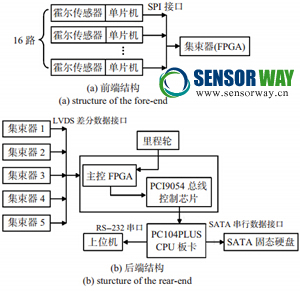

系统硬件组成可分为前端和后端两大部分,如图2所。

图2 系统前端与后端硬件结构图

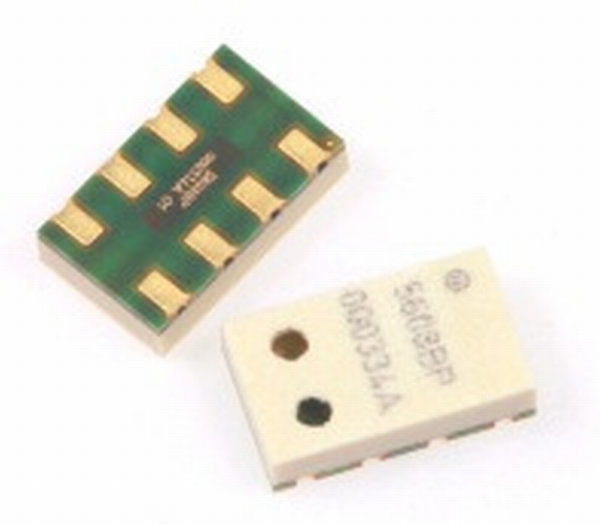

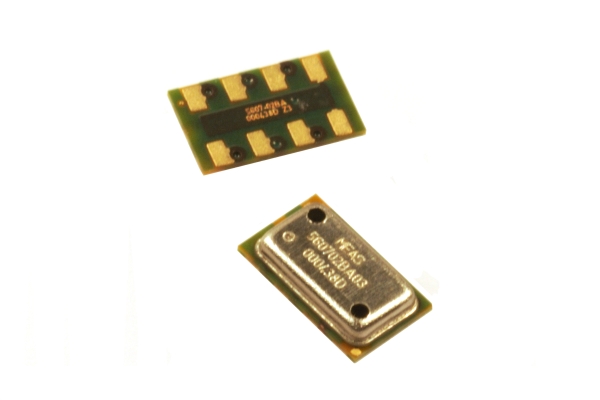

图2 (a)为前端数据采集结构,传感器采用可休眠线性 霍尔型传感器,具有5mV/Gs的

检测精度,由单片机控制探 头内5只传感器电压信号的A/D转换,转换精度为8位。集束器端FPGA选用Altera的Cyclonelll系列FPGA,主要 控制单片机的SPI传输和后端的LVDS串行传输。

图2 (a)为后端数据存储结构,PCI9054总线控制芯片 作为主控FPGA到PC104的总线控制器,使得PC104可以 直接通过PCI方式读取主控FPGA内部缓存数据。主控FPGA 选

用 ALTERA 公司的 Stratix 的 EP1S20F484I6 型芯 片,具有20k的LE逻辑资源,主控逻辑设计LE单元使用率达75% ;内部静态RAM大小为1.67 Mbit,可实现8位地址总线,32位并行数据总线的双缓存乒乓设计,以满足大量 数据的缓存要求。

3 系统逻辑设计

3.1总体逻辑设计

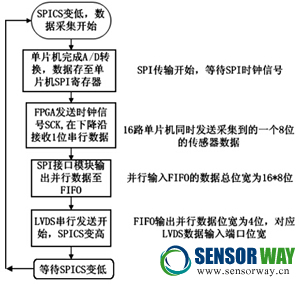

系统总体逻辑设计框图如图3所示。系统运行过程中,里程轮会随着检测器运行的距离变化发出周期性的方 波信号,主控FPGA通过倍频的方式使其满足设计要求的 采样频率,并行发送至前端数据采集系统,确保前端各单片 机同时进行A/D转换。探头内由单片机负责依次A/D转 换5只霍尔传感器感应到的磁通信号,通过SPI总线将采 集到的数据发送回集束器端的FPGA;5组集束器端的FP-GA通过LVDS串行收发器同时将前端数据发送到主控FP-GA,当主控FPGA内部缓存满后,发送使能信号到PCI9054 桥芯片,通知PC104工控机读取FPGA的内部缓存数据,并 将数据及时存储到固态硬盘设备中。

图3系统逻辑框图

3.2SPI总线接口模块与FIFO缓存模块

集束器端FPGA作为SPI总线传输的主机端,提供2 MHz的SPI时钟信号,16路单片机做为从机端,同时接收 SPI时钟信号并发送数据。基于本系统庞大的前端传感器 数量与单向的数据传输结构,只采用了主机输入/从机输出 数据线MISO, SPI时钟线SCK和使能信号线SPICS 3的三 线形式即可完成SPI传输。SPICS信号默认为高电平,会根 据里程轮方波信号翻转变为低电平,单片机接收到低电平 后开始A/D转换数据和SPI传输,在单次SPI数据传输中 SPICS始终保持低电平状态。通过设置异FIFO缓存模块 读写时钟和进出数据位宽,可协调SPI接收模块与钟和进出数据位宽,可协调SPI接收模块与LVDS发 送器数据不同位宽和数据传输频率不同的问题,前端SPI 数据传输的流程如图4所示。

3.3 LVDS差分串行收发器模块

根据内检测器结构设计,从集束器FPGA到主控FPGA 的信号走线距离为4~5m,这种长度的走线一方面对较高频率的数据传输信号衰减比较严重,另一方面会增加信号干扰,降低信噪比,严重会导致数据接收出错。因此,采用 差分信号进行两级FPGA之间的数据传输,它与普通单端 信号走线相比有3个明显的优势:抗干扰能力强、能有效抑制EMI、时序定位精确。

图4 前端SPI数据传输流程图

系统采用了 ALTERA公司提供的LVDS差分串行收发 器IP核,方便快捷地实现了差分串行数据传输:通过配置 LVDS发送器的端口位宽、通道数及传输速度,集束器端FPGA可将FIFO缓存输出的并行4位数据转为串行数据发送到主控FPGA,主控FPGA通过LVDS接收器将串行数据 解串为并行数据存入内部缓存中。串行收发器经实际测试 可达400 Mbps,远远满足系统数据传输速度要求。

4 漏磁检测数据分析

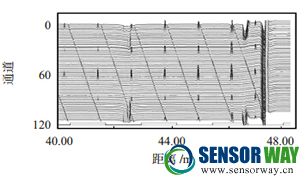

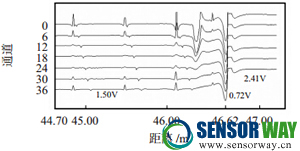

将管道内漏磁检测系统置于813 mm管径的直线测试 管道中进行牵引实验,管道总长118 m,运行平均速度为 1.2m/s,经上位机软件分析得出的各通道传感器数据如 图5,图6所示。

图5管道内漏磁检测原始数据图

图6 管道44.70~47.00m段7通道传感器数据分析图

图5为通过软件分析得出的40.00~48.00m的其中120路管道漏磁检测原始数据图,横轴

表示检测器运行距 离,竖轴从上至下为均匀分布在管道检测器外部圆周上的 各通道传感器漏磁数据,图下方为记录距离的里程轮方波信号。

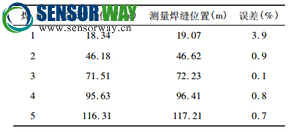

图6表示图5其中一段44.70~47.00m处管道的7个通道传感器数据图,管壁无缺陷处的电压值为1.5V,变化 范围为0~3V之间,46.62m处各路传感器信号电压值同时 下降到0.72V左右的位置应为管道该段的环焊缝所在位置。管道实际焊缝位置与系统测量得出的位置对比结果如 表1所示。

表1管道焊缝位置测量结果

从对比结果可知,测量出的管道焊缝位置与实际焊缝 位置基本一致,且通过分析各通道传感器电信号变化的长 度幅度,可如实反映出实际管壁上缺陷的大小深度,说明系 统数据传输存储稳定可靠,可实际应用于813 mm的大管径 管道的检测任务。

5 结论

本系统使用的Stratix系列的FPGA具有丰富的逻辑资 源,优秀的速度以及大容量的内部静态RAM,实现了多达 400路漏磁传感器信号的并行采集和快速存储,通过FPGA 的功耗分析工具优化系统逻辑设计,可使系统整体功耗低 于75W,与传统管道内漏磁检测系统相比大大降低了功耗, 使系统适应长距离的管道检测,实验结果充分证明了系统 数据传输的准确性,为管道检测及其他需求多传感器数据 采集存储的工程领域提供了一个值得借鉴的设计方案。(作者:尚林\李一博\陈世利\刘栋)

转载请注明来源:赛斯维传感器网(www.sensorway.cn)